在传统冯·诺依曼计算架构中,由于CPU与存储器的分离,数据在两者之间频繁地传输会产生巨大的功耗;同时,由于数据的访问速度跟不上CPU的处理速度,计算效率将受到严重限制。这称为“冯·诺依曼瓶颈”。近年来,随着忆阻器(memristor)的兴起,有研究人员提出采用忆阻器构建新型非冯·诺依曼计算架构。忆阻器的阻值能跟随流经的电荷量变化,在不同的电压操作下,阻值能在高阻态和低阻态之间发生翻转。撤去电压后,阻态能稳定保持,具有非易失性。如果把忆阻器的高低阻态看作计算机信息处理中的数据0和1,把外加电压的过程看作数据处理,则基于忆阻器的计算架构能够实现计算与存储的融合,有望突破“冯·诺依曼瓶颈”,进一步提升计算机性能。

图1. (a)传统冯·诺依曼计算架构与(b)基于忆阻器的计算与存储融合架构示意图,(c)在新架构中数据处理的操作模式

实验室在基于忆阻器的逻辑计算领域展开了深入研究,早期利用相变存储器件构建出非易失性“与”、“或”、“非”逻辑门电路(J. Appl. Phys. 114, 234503, 2013);随后在反向串联忆阻结构、交叉阵列集成结构和1T1R集成结构中,提出并实验展示了三步之内可实现任意二值布尔逻辑功能的方案(Appl. Phys. Lett. 106, 233502, 2015;ACS Applied Materials & Interfaces, 8(50), 34559–34567, 2016;IEEE Electron Dev. Lett. 38, 179-182, 2017);并提出了阵列可重构逻辑的可行方案(Nanoscale, 9, 6649-6657, 464, 873, 2017)。

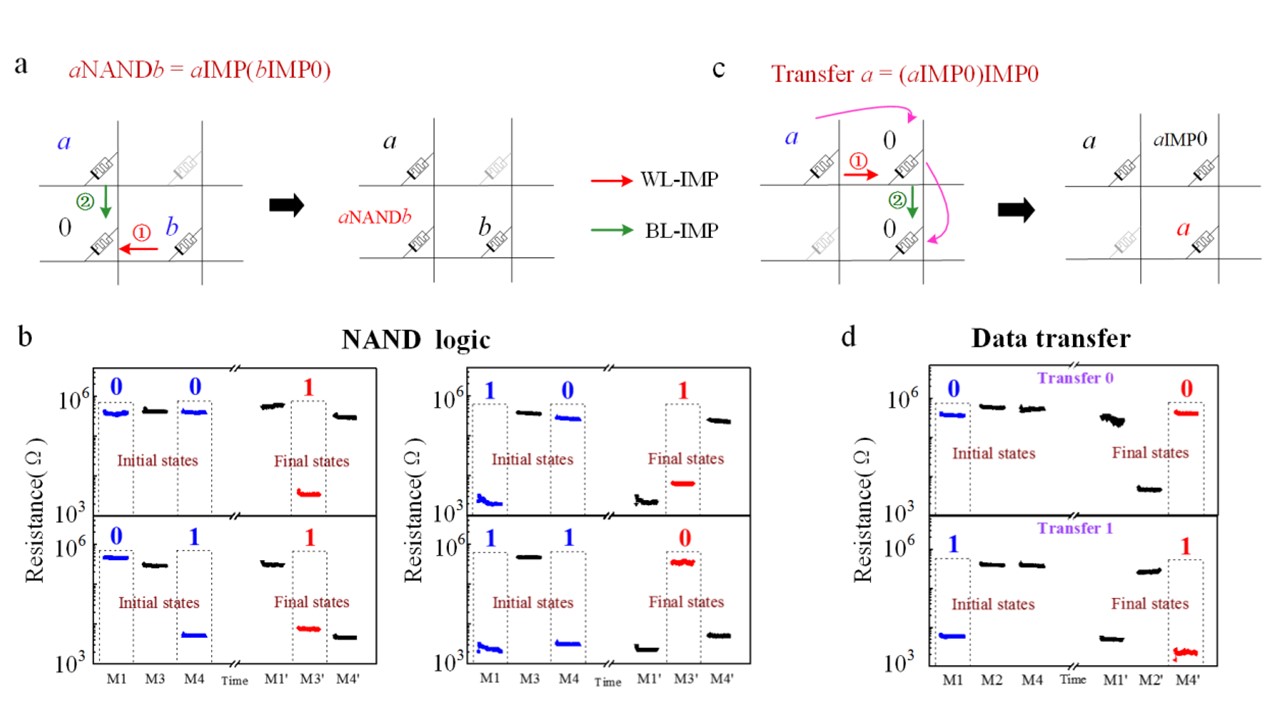

最近,我们将目光聚焦到忆阻阵列中实质蕴含逻辑(material implication logic, IMP)功能的实现与优化。实质蕴含逻辑是一种输入和输出都为非易失电阻的状态逻辑,能够进行逻辑级联,并通过迭代实现其他布尔逻辑功能,应用于忆阻逻辑电路中具有优势。2010年美国HP公司首次在忆阻单元中物理实现了该种IMP逻辑(Nature,2010,464,873)。然而,近年来如何利用IMP逻辑在规模阵列中进行功能的重构设计和优化,仍是一个值得深入探讨的问题。

在工作中,我们通过将Ti/HfO2/W忆阻阵列与电阻串联,实验验证了字线上和位线上的IMP逻辑计算功能,成功地在该结构中实现数据的写入、存储、读取、计算与传输一体化。通过将字线和位线操作方法结合,可以在2×2的最小单元结构中实现可重构的16种二值布尔逻辑;在一个2×4单元结构中,设计并仿真验证了一位全加器功能原理。数据处理的灵活性、级联问题、误码率问题也进行了探讨。该工作具有可重构、逻辑功能完备、计算资源灵活调度和高并行性特点,为构建基于实质蕴含非易失忆阻的大规模内存计算架构提供了一种可选方案。本研究中所使用的HfO2阵列为中科院微电子所提供。

图2. 2×2忆阻阵列中实现NAND逻辑运算及数据传输功能的实验结果

研究成果“Reprogrammable logic in memristive crossbar for in-memory computing”于2017年10月26日在线发表于Journal of Physics D: Applied Physics(doi: 10.1088/1361-6463/aa9646),程龙博士生为第一作者,李祎讲师与中科院微电子所龙世兵研究员为并列通讯作者。研究获得国家自然科学基金、国家重点研发计划纳米专项青年项目以及武汉市科技局项目的资助。