一、忆阻器电阻转变物理机制和高性能器件研制

忆阻器的电阻转变行为通常伴随着电子、离子等电荷的场致输运。

描绘器件中电子注入过程、迁移离子的类型、离子产生和复合的电化学反应过程,阐明电场作用下的纳米尺度器件中的电荷输运机制及其对器件导电特性的影响。

场致电子或离子的迁移会导致器件中局部区域元素分布、价态成键和材料结构等的变化,改变材料能带结构和电荷输运性质,从而在器件两端电极之间导致金属性导电通道的生长和断裂过程。

研究导电通道的动态演化过程,建立微观物理机制与宏观电阻转变特性行为之间的映射关系。

针对纳米尺度器件的性能要求和功能需求,理论预测并研发高性能忆阻材料体系(重点包括与CMOS工艺高度兼容的HfOx二元氧化物、SrTiO3多元复杂氧化物、GeTe和SbTe基硫系化合物),探索研究器件结构及低温集成工艺。

从材料匹配、器件结构设计、关键工艺、测试方法等多层面开发低功耗、高速器件的研制技术。

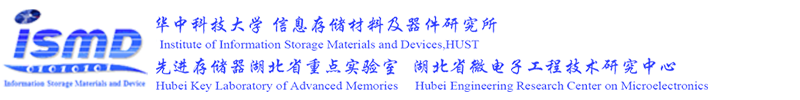

二、基于忆阻器的类脑神经形态计算

2014年12月19日美国《科学》杂志公布了其评选的2014年十大科技突破,其中美国国际商用机器公司(IBM)研制的新一代模仿人脑计算机芯片榜上有名。其后不久,这项科技突破也在中国科学院和工程院两院院士评选出的国际十大科技新闻中名列榜首。这款名为“真北(TrueNorth)”的芯片包含54亿个晶体管,根据人脑神经系统中神经元和神经突触结构和功能,“真北”模拟了100万个神经元和2.56亿个神经突触,具有4096个处理核。这些处理核相互连接,形成了一个如神经网络般的网状结构。这款芯片能够受到如此高的赞誉,在于其处理信息的模式是革新的,不同于传统的存储和计算分立的冯•诺依曼计算架构,“真北”能够模仿人脑的信息处理方式的。这意味着,信息的存储和计算不是在某个单独的单元处实现,信息在网络中传输的同时就完成了对它的并行式分布处理,或者说,信息的存储和处理不再存在明显的分界线,是融合的。这样一种仿脑计算架构和范式在并行处理大数据量的任务时,比如视觉捕捉、图形识别,能够表现出优越的性能,可能给大数据时代下需要应对海量实时数据的大规模并行运算计算机架构带来革命。

然而,需要指出的是,现阶段,神经形态芯片中突触的数目远远超过神经元的数目,人工突触占据了芯片的大部分面积,消耗了大部分功耗。研究人员开始竞相研发新型的人工突触器件,来突破神经形态芯片模拟人脑智能这一发展过程中的功耗和集成度瓶颈。理想的人工突触器件应该具有以下几种基本性能:1)具有非易失的突触权重;2)具有突触可塑性,即突触权重能够通过学习从而发生改变;3)纳米级尺寸;4)低功耗;5)易于大规模互连集成。只有拥有这样的人工突触器件,才可能开发出能够在一定程度上模仿大脑认知功能的微电子芯片,同时芯片面积和功耗在可接受范围内。

模拟生物神经突触的可塑性的首要条件是人工突触器件的电导(或电阻)可模拟式地连续调节,而忆阻器这样一种具有记忆功能的非线性电阻,其阻值能够随流经的电荷量而发生变化,并在断电后保持这种变化的状态,可以认为是模拟神经突触的完美器件。自2008年惠普(HP)实验室首次在TiO2材料中物理实现忆阻器,并声称忆阻交叉开关矩阵是唯一具备模拟人类神经突触足够密集度的技术之后,基于忆阻器的人工突触器件就迅速得到学术界和工业界的高度重视。

根据HP提出的TiO2忆阻器的氧空位边界迁移理论,器件电阻由富氧层电阻和缺氧层电阻共同决定。在外加电压作用下,氧空位迁移导致两层的边界发生迁移,从而导致器件电阻可以在高阻态和低阻态区间连续变化。当然氧化物忆阻器的阻变过程中氧空位的作用无法用此模型严格精确描述,譬如氧空位迁移引起导电通道的形成/断裂及导电通道的数量变化,或功能层/电极间界面势垒高度变化都可以使器件发生电阻渐变现象,但基于氧空位迁移的忆阻器确实能够展现出良好的电阻渐变特性,从而用于突触可塑性学习的功能实现。密歇根大学Wei Lu研究组的WOx,斯坦福大学H.-S. Philip Wang研究组的AlOx和HfOx,日本国立材料科学研究所Tsuyoshi Hasegawa研究组的Ta2O5和WO3-x,中国东北师范大学Zhongqiang Wang等人采用的InGaZnO,以及其他研究组的PCMO、Cu2O基等电子突触器件都是基于氧空位迁移原理来实现神经元电脉冲活动时间依赖突触可塑性(Spike-timing-dependent plasticity,STDP)功能。这一功能指如果突触前神经元活动(电脉冲释放)先于突触后神经元活动,将引起突触连结强度的增强,如果突触前活动迟于突触后活动,会产生抑制使突触连结强度减弱。这样的突触前活动和突触后活动时间先后次序对突触传递的影响已经被认为与脑学习和记忆功能直接相关。

在单个人工突触器件展示出类突触可塑性等仿脑认知功能后,要进一步推进人工突触器件的研究和应用,必将探讨具有一定规模互连的、基于新型忆阻突触器件的神经网络电路的构建以及更高阶认知功能的实现等重要问题。其中,能否基本认知存储器件,与传统电学元器件配合,以优化传统晶体管神经电路的复杂度和能耗,以更简洁高效的形式实现传统VLSI方法中极为复杂的仿脑认知功能,这是忆阻突触器件能否在未来神经形态工程中发挥核心作用所要面对的极为现实的挑战。

同时,国内外研究人员在忆阻神经网络领域也做了不少开创性工作,实现了字母、手写字体、人脸图像等模式识别功能。

基于已有研究基础,团队拟进一步深入研究氧化物及硫系化合物忆阻突触器件及脉冲神经网络。重点研究纳米尺度下忆阻器中场致输运行为、导电机制及其对忆阻特性的调控规律。揭示微观忆阻物理机制和演化过程与宏观认知功能之间的内在联系。进而,根据神经生物学中突触可塑性与网络级高阶学习功能间的内在联系,来设计基于忆阻突触器件的脉冲神经网络,实现模式识别等认知功能。研究将为进一步优化设计忆阻突触器件奠定基础,并为忆阻突触器件应用于未来大规模、多样化的神经形态电路系统和人工神经网络中提供方法和技术指导。

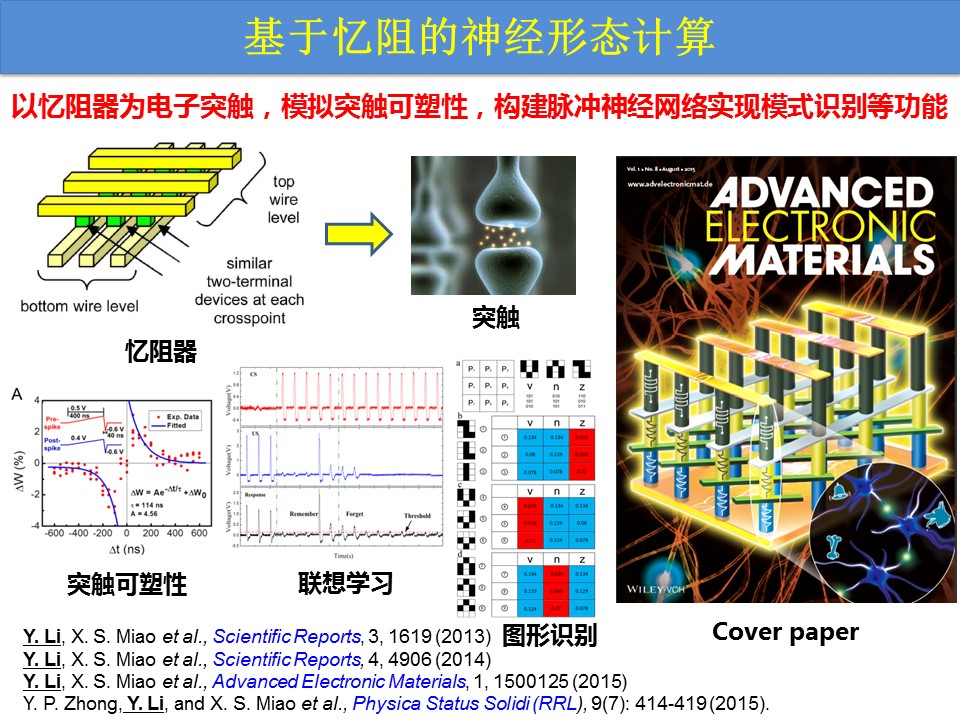

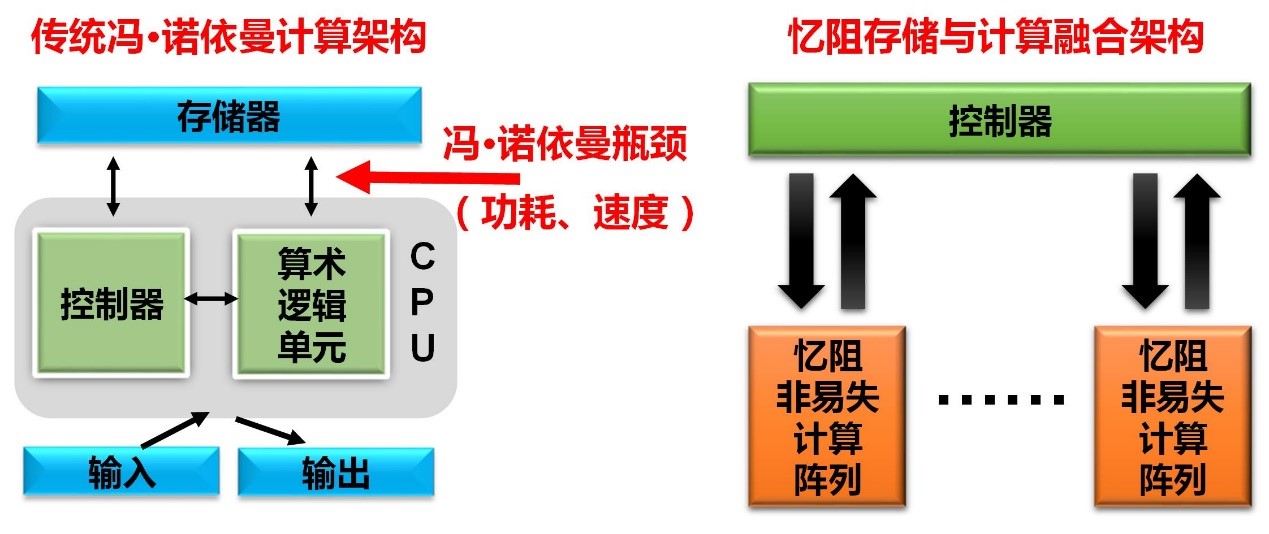

三、基于忆阻器的非易失逻辑运算技术

忆阻器,是电阻、电容、电感之外的第四种电路基本元件,具有高速、低功耗、高集成度、兼具信息存储与计算功能等特点,被认为是最有潜力的未来逻辑运算器件,将推动逻辑运算理论与计算体系结构的全面变革,为从根基上颠覆传统冯·诺依曼计算架构和整个计算机体系奠定器件基础。

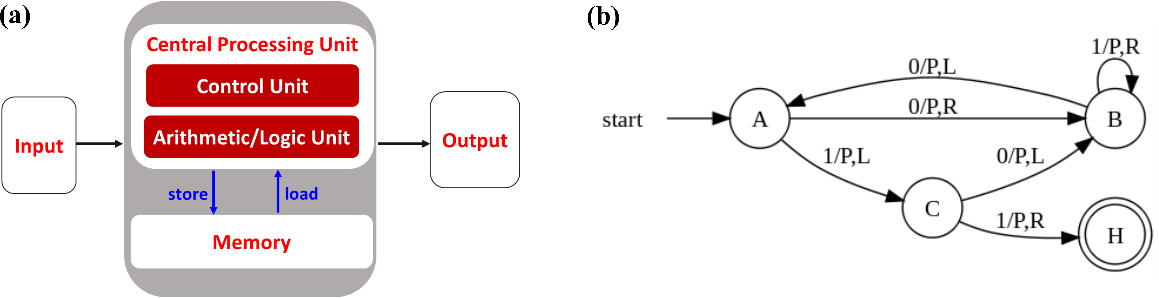

图2 传统冯·诺依曼计算架构与未来忆阻计算架构对比

图3 非易失逻辑运算和神经形态计算都被IRDS列为未来重要的非冯诺依曼计算技术

研究目标:基于忆阻器、阻变存储器等新型纳米信息器件,设计非易失性基本布尔逻辑电路和运算方法,构建组合及时序逻辑电路,为发展未来存储与计算融合的内存计算技术提供候选器件方案,进而提出新型高性能并行计算技术。

团队于2013年利用硫系化合物相变器件构建了“与、或、非”三种基本布尔逻辑电路,提出了利用器件二值阈值开关特性实现逻辑运算功能的原理,并在Ge2Sb2Te5存储器件中获得实验验证。与传统CMOS晶体管电平逻辑不同,在存储器中直接进行逻辑运算时,用来表征0和1逻辑状态的运算变量不仅可以是电平信号,还可以是器件的电阻状态。而且,逻辑运算的结果非易失性地保存在器件电阻状态之中。该研究为发展未来存储与计算融合的内存计算技术提供了新的候选器件方案,以题为AND, OR, NOT Boolean logic in phase change memory发表在Journal of Applied Physics, 114, 234503, 2013。

在此基础上,进一步研究发现了[GeTe/Sb2Te3]n超晶格存储器件的磁电耦合效应,在电平、电阻之外,引入磁场强度作为新的逻辑输入变量,成功实现了7种布尔逻辑运算功能。该研究为未来非易失性逻辑运算器件和电路提供了新思路,以题为Logic gates realized by nonvolatile GeTe/Sb2Te3 super lattice phase-change memory with a magnetic field input发表在Applied Physics Letters, 109, 023506, 2016。

在探索非易失性逻辑运算器件基础上,团队基于不同忆阻器单元和集成结构,在非易失逻辑运算算法和实现方面也取得了一系列重要进展。

团队首先从二值布尔逻辑代数原理出发,提出了一种通用逻辑算法。该算法核心是一个数学表达式,表达式中的逻辑输出由四个数学变量输入所共同确定。通过改变四个数学变量的赋值排列组合,可以推导出完备的16种布尔逻辑。在物理器件中,通过赋予四个数学变量以实际物理参数涵义,即可实现所需的逻辑功能。基于以上思路,团队利用以开关速度达5 ns的Ta/AgGeTe/Ag高速双极性忆阻器为基本单元集成在目前主流的crossbar高密度交叉阵列之中,以初始化电阻状态、器件两端脉冲电信号、电信号极性为四个变量,在单个器件中两步内即可实现任意布尔逻辑。与现阶段相关国际报道文献相比,其计算复杂度最优,且兼容高密度阵列集成方案。相关结果以题为Realization of Functional Complete Stateful Boolean Logic in memristive crossbar array发表在ACS Applied Materials & Interfaces, 8, 34559–34567, 2016。

之后,团队与我校客座教授、台湾中山大学张鼎张教授合作,以忆阻器件的初始化电阻、晶体管的源、漏、栅极电压为四个数学变量,实验验证了所提出逻辑算法的通用性。该工作进而探讨了1T1R非易失逻辑门的级联方案,进一步提升了忆阻逻辑技术的实际应用可能性。相关工作发表以题为Functionally complete Boolean logic in 1T1R resistive random access memory发表在IEEE Electron Device Letters, 38, 1-4, 2017。

此外,该逻辑算法也可针对互补式结构忆阻器的电学特性进行变量赋值上的灵活调整,相关结果以题为16 Boolean logics in three steps with two anti-serially connected memristors发表在Applied Physics Letters, 106, 233502, 2015。

为解决时序状态逻辑迭代和资源充分分配问题,团队探索了忆阻器阵列中逻辑迭代、逻辑状态的转换输出与原位级联,为非易失性忆阻逻辑的阵列化并行计算提供了可行方案。研究中灵活利用交叉阵列中最常见的单个双极性器件和两个反向串联的互补式拓扑结构,通过输入信号的相应设计,在同一单元中可实现八种不同的基本布尔逻辑,如重要的NAND、NOR,并提出了全加器实现方案。相较于传统可重构逻辑电路,忆阻逻辑功能进行重构时,无需进行硬件连接的改变,而只需通过控制信号的调控。这就意味着通过低成本的大规模阵列制备,即可获得灵活的功能重构和计算资源的优化配置,结合新颖的运算结构非易失性原位存储功能,可作为未来高性能并行计算的潜力方案。相关工作以题为Nonvolatile reconfigurable sequential logic in a HfO2resistive random access memory array发表在Nanoscale, DOI: 10.1039/c7nr00934h, 2017,并被选为内封面论文。

另外,针对逻辑电路设计中常用的CMOS布尔逻辑电路,团队设计了仅由四个晶体管和一个忆阻器构成的XOR逻辑门,在电路结构和功耗上有较大优化,为新型全加器、图像识别的硬件实现提供了新的硬件解决方案。相关工作发表在Physica Status Solidi A, 213, 1050-1054, 2016。

四、神经形态计算(Neuromorphic computing)

在大数据时代,数据信息呈爆炸式增长,信息系统追求越来越快、同时也越来越智能的信息处理与存储。然而传统的计算机是依据冯·诺依曼计算架构与图灵机两大概念建立的。在冯·诺依曼计算架构中计算和存储功能是分离的,两者速度的不匹配形成了冯·诺依曼瓶颈,且这一差距被越拉越大,限制了信息处理速度和效率的进一步提高。另一方面,图灵机的状态跳变是预先确定好的控制规则进行,即它不具有自主学习能力。

图4:(a)冯·诺依曼计算架构(b)图灵机原理

神经形态计算借鉴人脑的认知信息处理模式,信息的处理与存储依靠神经元与突触均在神经网络中完成,这就实现了存储计算融合(In-memory computing),克服了冯·诺依曼瓶颈问题。并且,神经形态计算模仿大脑中突触的可塑性,具有自主学习的能力,即现在炙手可热的人工智能(Artificial Intelligence)。因此,神经形态计算被近年来的国际半导体技术路线图钦定为下一代信息技术的两大候选之一。

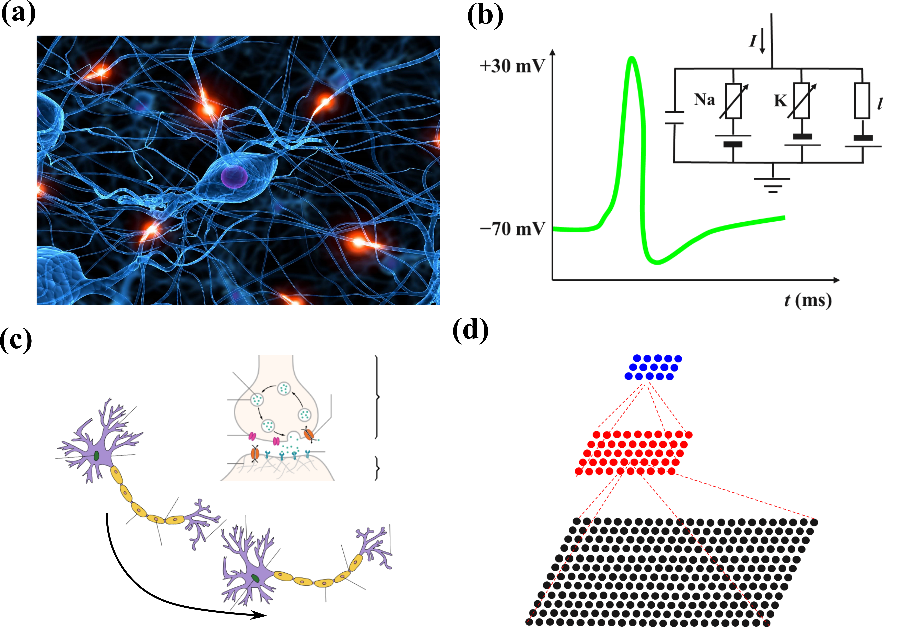

图5:神经形态计算原理图(a)生物体中的神经网络示意图:蝌蚪状蓝色小球表示一个神经元,蓝色小球之间连接的火花代表神经元之间的突触正在传导信号。(b)神经元的积分点火(Integrate-&-Fire)工作模式示意图。(c)突触可塑性的Hebb法则。(d)多层(multilayer)前馈(Feedforward)神经网络示意图。

当前,神经形态计算研究大体可以分为顶层的算法设计(Algorithms)与底层的器件开发(Devices)。我们研究组致力于开发基于脉冲神经网络(Spiking Neural Network)的底层神经形态器件与顶层人工智能。

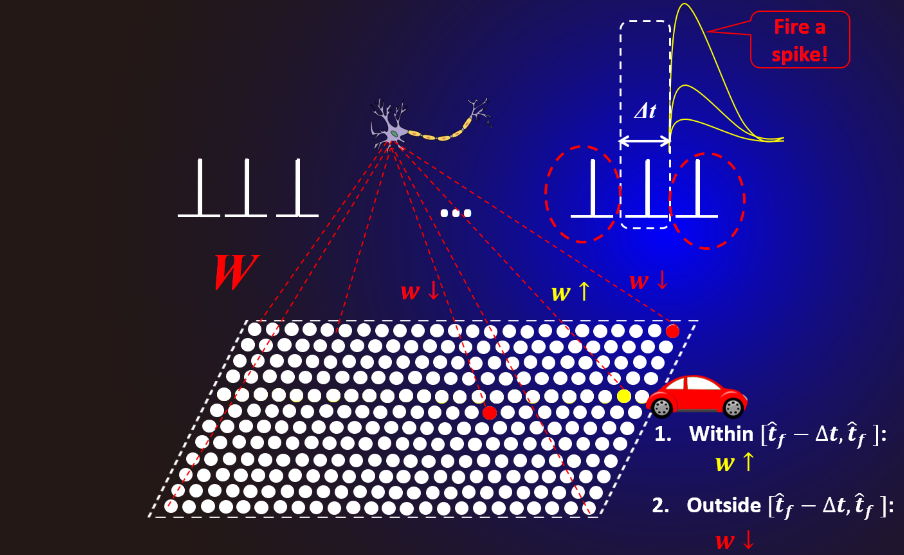

图6:基于脉冲神经网络的运动模式识别原理图(详细介绍见ppt)

底层神经形态器件是指能够模拟突触与神经元功能的人工器件。突触仿真一项最重要的功能是基于脉冲时序的可塑性(Spike-timing dependent plasticity,缩写STDP),根据顶层算法的不同,STDP具体表现形式也不同,并不拘泥于生物学突触的表现形式,如下图所示。

图7:基于脉冲时序的(突触)可塑性有多种表现形式。横坐标是前突触神经元脉冲与后突触神经元脉冲的时间差,纵坐标是突触权重(synaptic weights)的相对变化。

同样道理,人工神经元器件并不追求全盘模仿生物神经元功能,而是根据上层算法的要求,选择性实现如积分-点火(Integrate-&-Fire)、不应期(refractory period)、激发/抑制(Excitatory/inhibitory)等功能。

综上所述,我们研究组针对某项具体的人工智能(如运动模式识别、语音识别等),设计基于脉冲神经网络的算法,并采用软硬件结合的手段优化神经网络设计,并据此指导底层人工突触与神经元器件的研发、组网。

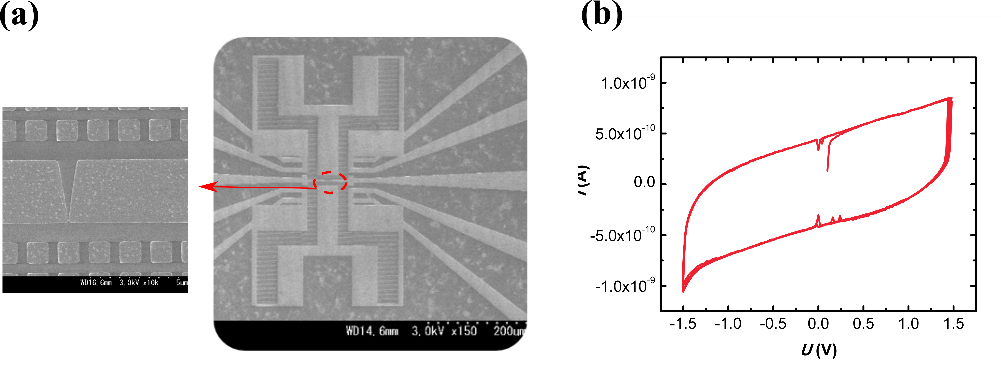

图8:基于纳流体的突触器件原型(a)采用微纳电子工艺制备的纳流体沟道。(b)纳流体沟道的伏安特性曲线扫描图,包含显著的记忆特性。

更多详细介绍参见何毓辉博士讲授《微电子学前沿报告》课件(2017年):

Synapse, Neurons & Brain-inspired Computing(突触、神经元与类脑计算)