相变存储器是基于硫系化合物非晶和多晶之间的快速相变来实现信息存储的。研究所对相变机理、材料、工艺、测试和集成均有深入的研究,相变存储器被认为是目前解决闪存到达其物理极限问题的下一代非易失性存储器的主流产品之一。据美国ECD公司分析预测,相变存储器若能大批量生产,将能在世界年产值为1400亿美元的巨大器件市场占很大份额。

目前的研究主要集中在:

1.低功耗、低串扰相变存储材料及其存储器研究:包括低密度变化、低热串扰、超晶格、纳米相变材料等;

2.高存储密度的相变存储器研究:包括多值相变存储器,3D X-Point等。

在国家863重大项目、863主题项目、863面上项目、国家国际科技合作项目、国家自然科学基金面上项目、总装备部预先研究项目、国家外专局重点项目、湖北省科技攻关重大项目、武汉市科技攻关项目以及东湖高新区设备专项等资助下,华中科技大学取得的重要成果包括:

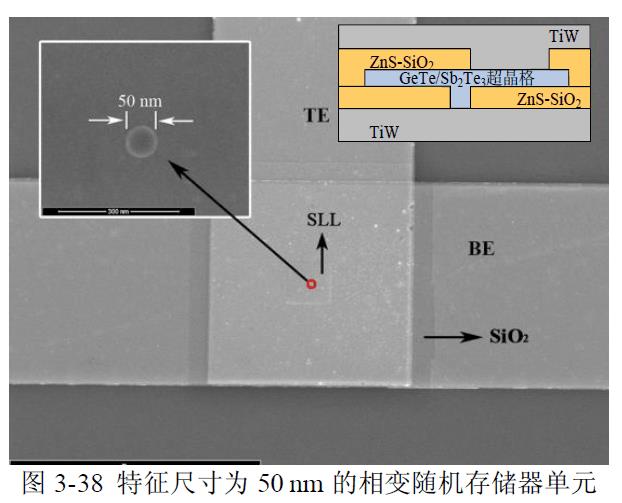

1. 成功研制出我国具有完全自主知识产权的256b相变存储器功能芯片(2009年)和1Mb相变存储器测试芯片(2010年),其外围电路在中芯国际0.35和0.18微米CMOS集成电路生产线上流片。其中1Mb相变存储器单元Reset速度优于国际文献报道水平,研究成果作为与浪潮合作的“海量存储系统关键技术”重大成果的一部分参加了“十一五”国家重大科技成就展。

2. 研究出了与标准CMOS工艺兼容的相变存储器加工工艺。

3. 研究成功的相变存储器存储单元,其RESET速度最快可达0.2纳秒,优于国际文献报道。

4. 基于中芯国际65纳米CMOS工艺设计了1Gb相变存储器芯片。

目前拥有国际/中国专利、集成电路布图设计专有权、软件著作权等40余项。

研究成果受到来武汉光电国家实验室视察的习近平、胡锦涛、吴邦国、温家宝、贾庆林、刘延东等党和国家领导人的高度关注。并作为“海量存储系统关键技术”重大成果的一部分参加了“十一五”国家重大科技成就展。

相变存储器

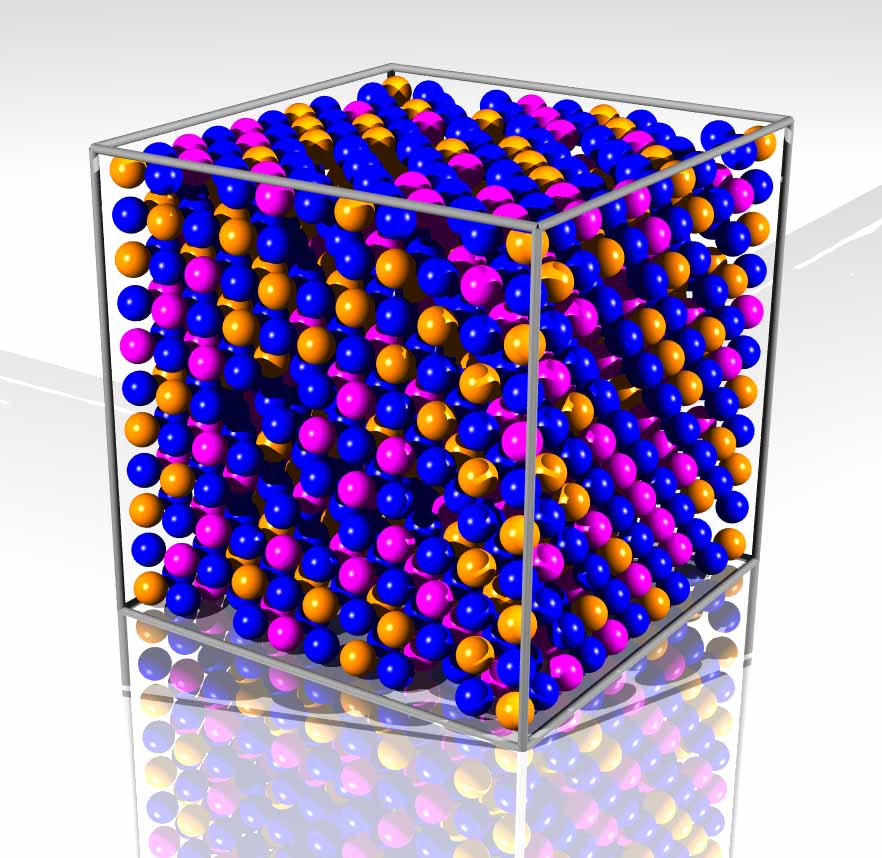

低密度变化 由于相变材料中存在大量的本征空位缺陷(例如,在Ge2Sb2Te5中约含10%左右的vacancies)。当晶体在熔化和快速冷却形成无定形态的后,这些本征空位聚集成几个原子大小的且形状不定的微空洞(voids)。通过计算发现,这些空洞的含量达到了16%~17%甚至更高,所以在相变的过程中存储单元会有6-8%的体积变化,使得相变材料的晶态和非晶态存在较大的密度差异。这种密度的变化会在器件内部产生应力,严重降低存储介质的稳定性,大大缩短器件的寿命。同时,在平面微缩实现器件高密度集成这一传统方法遭遇瓶颈的情况下,器件结构往三维方向的扩展成为实现高密度集成的必然选择。。按照不同的集成方式,三维交叉阵列可以分为将平面交叉阵列多层堆叠的3D X-point结构以及与BICS 3D NAND类似的垂直交叉阵列结构(3D VRRAM)。三维堆叠的器件结构在提升存储密度的同时,也会带来稳定性方面的问题。在高密度存储单元中,每个存储单元大小达到纳米量级,器件在相变的过程中承受的应力更大甚至会影响相邻的存储单元。更为严重的是,在多次擦写过程中,存储单元出现小的空洞,这些空洞会在电极处聚集,使得相变材料和电极的接触性能变差,最终导致了器件的失效。

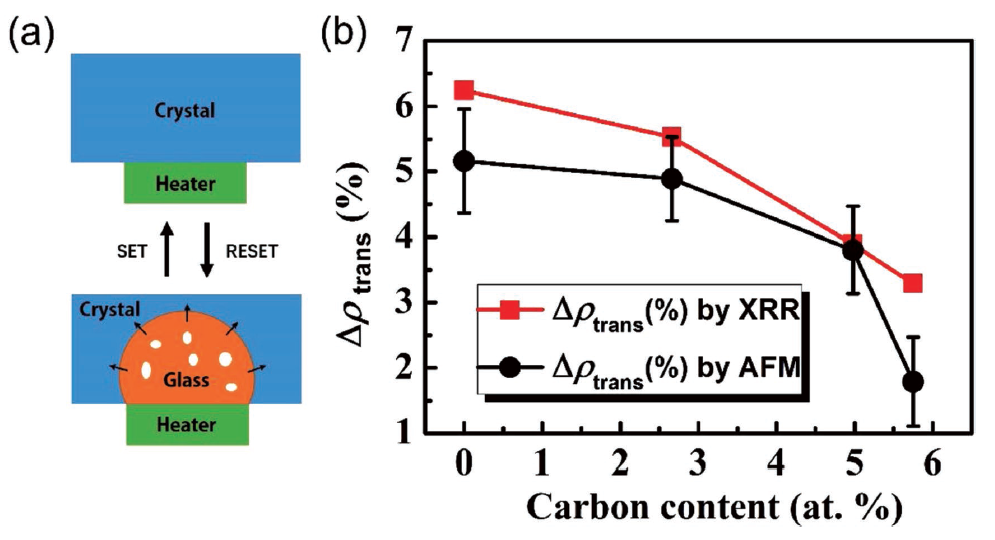

为了延长该存储器的寿命,研究所利用第一性原理计算对材料进行了筛选。建立了一批不同材料、不同掺杂的相变材料模型,通过计算比较晶态和非晶态的密度差异,以得到性能较优的材料GeSb。利用磁控溅射等薄膜制备方法生长获得若干上述的非晶材料,将部分样品退火获得材料的多晶态,用反射X光(XRR)和原子力显微镜(AFM)测量薄膜的密度变化(厚度变化),比较晶体和非晶的密度差,通过实验发现,在Ge-Sb中掺杂一定量的C时,能够将密度变化从6%降低到3%,如图1。

图1 a) 由于相变存储材料中晶体和非晶的密度差,在擦写区域会产生应力和一些小的空洞,这些空洞的聚集最终会导致器件的失效。b) 我们开发的新材料将晶体和非晶的密度差从原来的6%降低到了3%左右,有望显著提高存储器的擦写次数。

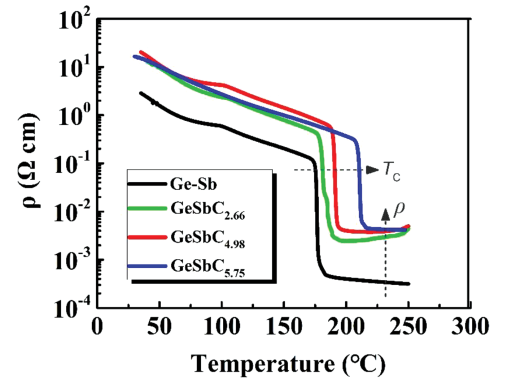

并进一步通过退火实验保证其能发生相变并保持一定的电阻窗口,同时掺C还能有效提高GeSb的晶化温度和晶态电阻率,提升了器件的稳定性,降低了其功耗,如图2。证明掺C的确是一种有效降低GeSb密度变化并保持其性能的手段。

图2 掺杂后的材料保持2个数量级以上的电阻变化,同时结晶温度和晶态电阻得到提升,证明掺杂可以同时提高非晶态稳定性和降低功耗。