现有计算系统大多基于晶体管器件和冯·诺依曼计算架构,正面临理论和技术瓶颈:1)晶体管微缩的摩尔定律行将失效;2)架构中存储与计算分离,“存储墙”和“冯·诺依曼瓶颈”问题严峻。发展高性能、存算一体化的新原理器件和新计算架构将成为能否突破的关键。2016年国际器件与系统发展路线图(IRDS)提出在存储器内执行计算的存算一体化技术是非冯计算技术的强有力竞争者。相较于传统CPU/GPU,一体化架构由大量非易失性存算一体化器件组成,通过可重构的原位并行计算和存储,大幅减少信息处理过程中的数据传输,克服带宽、延时和功耗瓶颈问题。

忆阻器(Memristor)于1971年由加州大学伯克利分校蔡少棠教授理论提出,2008年由美国惠普(HP)实验室在TiO2器件中物理实现。忆阻器因其非易失电阻转变特性可用作新型存储器,又能够执行逻辑运算和矩阵运算等基础运算,具有高速、低功耗、高集成度等优势,最有潜力成为存算一体化的基础器件。Nature Electronics展望文章将存算一体化忆阻器列为微电子三大未来技术之一。

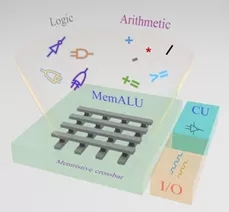

华中科技大学光学与电子信息学院、武汉光电国家研究中心李祎副教授、缪向水教授团队对这一新兴技术进行了深入细致的研究,与台湾中山大学张鼎张教授团队合作,提出了基于忆阻器阵列的非易失算术逻辑运算单元(MemALU)设计,在实际器件中实验实现了基本布尔逻辑与算术运算功能,相关结果发表在Advanced Functional Materials(DOI: 10.1002/adfm.201905660),论文第一作者为博士生程龙。

研究团队基于忆阻器的电阻转变行为,提出了一种优化的电压操作方式,仅使用一对幅值相同的正负电压,可以在忆阻器交叉杆阵列中可重构实现IMP、NOR、OR等多种状态逻辑功能,以忆阻器的电阻态作为逻辑输入和输出,实现非易失信息处理,在制备的Pt/HfO2/TiN忆阻器阵列中得到实验证实。该方案支持字线逻辑操作和位线逻辑操作,使信息灵活处理,对电压源数量的要求较低,且降低了最大操作电压。基于基本逻辑功能,其他布尔逻辑功能最多可在五个忆阻器中五步实现。除此之外,根据忆阻器阵列的结构,以及状态逻辑功能操作的特点,支持多行并行计算的N位全加器,高效率的递增、递减和移位等基础算术运算功能也得到实验和仿真验证。更具代表性的减法、乘法和除法等信息处理方式也由上述功能设计实现,证实了基于忆阻器阵列的非易失算术逻辑运算单元在功能上的可行性。

该工作为未来存算一体化技术提供了备选方案,为非冯计算系统的构建提供了逻辑算法支持。相关工作得到了国家自然科学基金以及国家重点研发计划的资助。

原文链接:

https://onlinelibrary.wiley.com/doi/10.1002/adfm.201905660