由于优异的器件性能,FinFET已经成为当前的主流逻辑工艺,台积电和三星等公司已经量产了7nm FinFET,并且已经朝着更小的器件尺寸进发了。然而由于器件尺寸的微缩,以及FinFET的3D漏源结构,其漏源的寄生电容电阻越来越不可忽视且复杂。在7nm节点,FinFET的寄生电阻可以达到45%,因此,对FinFET漏源寄生效应进行建模研究是一个十分必要的工作。

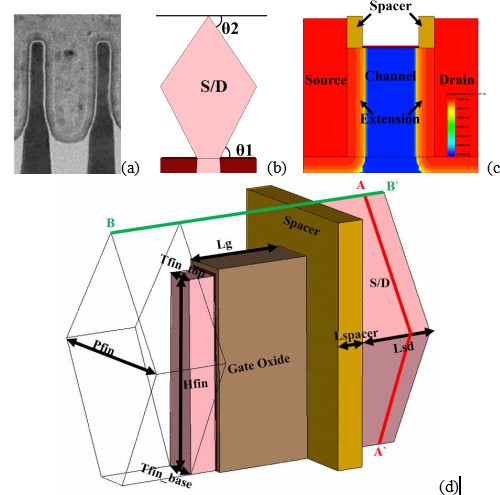

图一: 纳米尺度FinFET建模。

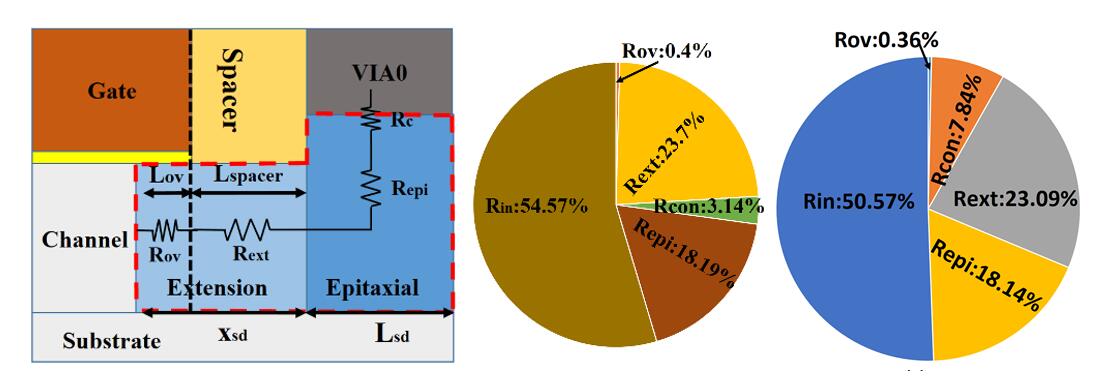

我们使用新思科技捐赠的Sentaurus TCAD工具对7nm FinFET进行了细致的TCAD建模,并且与 Globalfoundries/Samsung的真实器件结构以及I-V曲线进行了比对以及校准。根据真实的器件结构,我们从器件的物理原理出发,建立了一个3D的7nm及其以下节点的漏源寄生电阻紧凑模型。该模型主要将漏源寄生电阻划分成4个部分,accumulation resistance (Rac),extension resistance (Rext),epitaxial resistance (Repi) 以及contact resistance (Rcon).

图二: (a) 源漏电阻分解示意图;(b) 7纳米FinFET与 (c)微缩至5纳米的FinFET的源漏电阻。

完成建模后,采用7nm FinFET TCAD仿真平台对该模型进行验证,发现该模型的总体误差在4%以内。同时,我们将器件微缩到5nm以及3nm节点,发现器件的寄生电阻在总电阻所占比例,也即饱和电流的衰减程度,可以达到49%和52%。由此可见,寄生源漏电阻对于纳米节点晶体管产生严重影响,必须引起足够的重视。

论文已经被IEEE Transactions on Electron Devices接收,硕士生吴涛为第一作者,由研究所王兴晟教授、缪向水教授和英国格拉斯哥大学Asenov教授合作指导完成。

相关论文:

T. Wu, H. Luo, X. Wang, A. Asenov and X. Miao, "A Predictive 3-D Source/Drain Resistance Compact Model and the Impact on 7 nm and Scaled FinFETs," IEEE Transactions on Electron Devices, doi: 10.1109/TED.2020.2988858.

论文连接:https://ieeexplore.ieee.org/document/9085906