非易失性忆阻器存算一体化计算,不同于现有以晶体管为基础的易失性电平逻辑计算,它通过引入非易失性的物理变量(如电阻)参与运算,基于器件及阵列中的欧姆定律、基尔霍夫定律等物理定律来执行计算,能有效克服冯.诺依曼架构中存算分离的瓶颈问题,被认为是一项具有巨大应用潜力的高能效计算的颠覆性技术。

华中科技大学光学与电子信息学院信息存储材料与器件研究所团队致力于基于忆阻器阵列的存内计算研究。近日,团队在基于忆阻阵列执行异或(XOR, exclusive or)逻辑计算的新进展以“Two Memristors-Based XOR Logic Demonstrated With Encryption/Decryption”为题发表于微电子器件领域权威期刊IEEE Electron Device Letters,并被选为2021年9月刊的编辑精选(Editors’ Pick)文章。博士研究生宋玉洁、硕士研究生吴绮雯为共同第一作者,王兴晟教授为通讯作者。

异或电路在计算电路、数字信号传输的纠错电路以及编码加密中起着关键作用。在计算电路中,异或电路恰好可用于二进制数字电路中的加法运算,得出两个一位二进制数相加后的低位数值,称“半加器”。在密码学领域,XOR 运算有一个很奇妙的特点:如果对一个值连续做两次XOR,会返回这个值本身。XOR的这个特点,使得它可以用于信息的加密。同时,异或相比加减乘除这些加密操作额外的好处在于执行效率极高:它不会产生进位,各个部分间可以并行执行。XOR在编码学上也用的非常多的用途,特别是各类纠错码和校验码的编码关键过程。

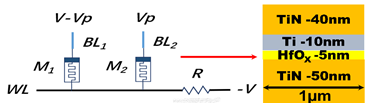

图1. 提出的基于TiN/Ti/HfOx/TiN忆阻器的异或电路

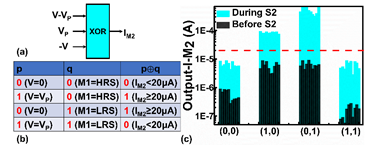

本工作基于忆阻器crossbar阵列,提出以两个忆阻器和一个分压电阻为基本结构单元(图1),仅用两步即可完成异或计算操作。如图2.(a)所示, T1、T3端的V代表输入信息p,第一个忆阻器的电阻状态代表输入信息q,经过T1、T2、T3三端电压配置后,计算后的结果p⊕q以电阻形式原位存储在第二个忆阻器中。图2.(c)展示了实测的计算结果。

图2. (a)表示输入输出信号的等效框图;(b)异或逻辑的真值表,表示逻辑输入/输出和物理输入/输出之间的映射关系;(c)四种输入输出的异或计算结果

另外,基于此异或电路演示了对15位像素灰度数据“DATA”的并行加密解密的计算结果(图3)。可以看出经过一次异或操作后,原图像信息无法分辨,加密成功;经过第二次异或操作后,重现了“DATA”,完成解密。进一步地,对串行和并行这两种在忆阻器阵列上的规划映射以及器件参数对计算结果的影响进行了深入探讨。

图3. 基于异或电路的加密、解密并行运算结果

相关横向计算对比表明,与传统的CMOS异或运算电路以及目前发表的基于忆阻器异或逻辑计算电路比较,本文提出的方案在电路面积开销、运行功耗以及运算延时等方面都有显著的性能提升。

该工作获得了国家重点研发计划项目(Grant No. 2019YFB2205100) ,国家自然科学基金项目(Grant No. 61841404),湖北省先进存储器重点实验室的支持。

论文信息:

Y. Song, Q. Wu, X. Wang, C.Wang and X. Miao, "Two Memristors-Based XOR Logic Demonstrated withEncryption/Decryption," in IEEE Electron Device Letters, vol. 42, no. 9,pp. 1398-1401, Sept. 2021, doi: 10.1109/LED.2021.3102678.

网页链接:

https://ieeexplore.ieee.org/document/9507424