近日,研究所王兴晟、缪向水教授关于忆阻器存算一体化颠覆性技术的最新研究结果发表在著名综合性学术期刊《Advanced Science》,题为“Reconfigurable and Efficient Implementation of 16 Boolean Logics and Full-Adder Functions with Memristor Crossbar for Beyond von Neumann In-Memory Computing”,我校为论文第一和通讯单位,王兴晟教授为论文通讯作者,博士生宋玉洁为论文第一作者。

延迟、能耗、面积是数据处理器的主要性能指标,随着物联网的普及,边缘计算设备数量庞大,需要计算和存储海量数据,使得低功耗计算成为关键的诉求。因当前主流的冯·诺依曼计算架构固有的存储单元与计算单元分离,导致数据在存储和计算单元之间频繁搬移,对处理器主要指令的使用频率的统计数据表明,数据搬移是使用频率最高的指令类型,数据在高速CPU和低速内存之间来回搬移,存和取造成了几倍于实际计算过程几个数量级的时延,另外,数据迁移能耗比计算能耗高一到两个数量级,造成了巨大的能量消耗。

区别于现有以晶体管为基础的易失性电平逻辑,非易失性存算一体化技术首先在原理上存在本质差别。通过引入非易失性的物理变量(如电阻)参与运算,基于器件及阵列中的欧姆定律、基尔霍夫定律等物理定律来执行计算,都是现阶段可预见的高能效计算解决方案。当前文献报道的忆阻逻辑运算、算术运算和矩阵运算等方案中,大部分工作只能支撑单一计算方法的物理实现,在应用方向存在局限性,这严重制约了忆阻器存算一体化技术的发展。此外,现有技术方案运算效率低,且未有成熟、系统、公认的计算理论和方法。因此发展高能效、功能可重构的忆阻计算理论和电路是本工作的核心研究内容。

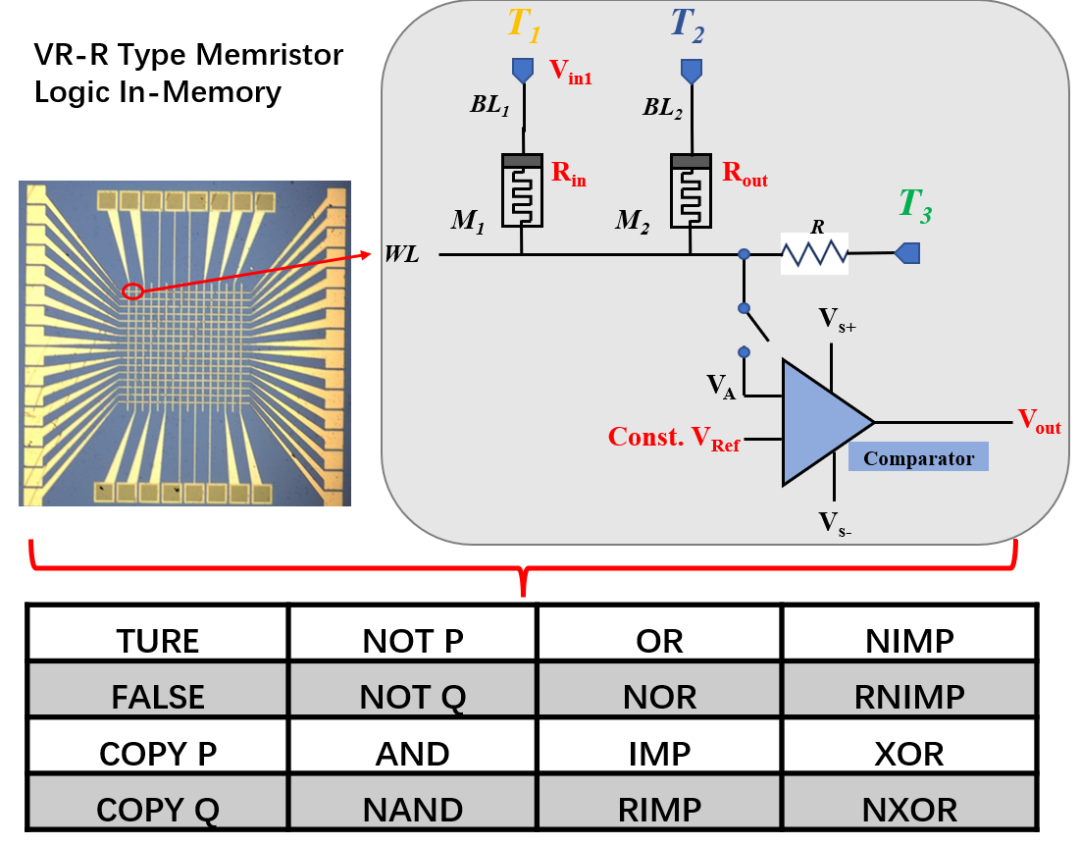

研究团队研发了高性能Ti/HfO2/TiN二值忆阻器,在8英寸晶圆流片实现了规模集成。基于忆阻器的电阻转变行为,研究团队提出了以V/R-R型“两个并联忆阻器再串联一个电阻(2M1R)”的新型逻辑计算基本结构为基础,进行推导验证,通过端电压配置,两步操作实现完备的布尔逻辑计算功能,从而克服以前忆阻器逻辑计算方案中存在的缺陷和不足,本工作电路单元结构简单且统一,计算步骤少,逻辑门可级联,寻址简单,对电压源数量的要求低,且降低了最大操作电压。在制备的Ti/HfO2/TiN忆阻器阵列中实验证实了可重构逻辑方案的可行性。

图:本工作提出的基于忆阻器的存内逻辑计算电路

该工作为未来存算一体化技术提供了备选方案,在存内逻辑计算领域取得重要突破,为非冯计算系统的构建提供了逻辑算法支持。未来有望在复杂逻辑拆分和高效硬件映射、高能效存储算术逻辑一体化单元(MALU)复杂架构和设计方法等方面做出新的贡献。

该工作获得了国家重点研发计划项目(Grant No. 2019YFB2205100)、湖北江城实验室、湖北省先进存储器重点实验室的部分支持。

论文信息:

https://onlinelibrary.wiley.com/doi/10.1002/advs.202200036